# **Development of Intelligent Power Device SIP1 Series**

Hiroaki Kawaguchi\*

Abstract Automobiles are undergoing a period of major change, including electrification, automated driving, and connectedness, and with these changes, the E/E architecture of automobiles is undergoing a rapid shift from a functionally distributed architecture to domain-type and zone-type architectures.

In the zoned E/E architecture, it is expected that the conventional power distribution system using mechanical relays and fuses will be replaced by a power distribution system using semiconductors such as IPDs. We report on the development of the next-generation automotive IPD "SIP1 Series," which incorporates the functions required for next-generation zoned power distribution systems.

In the next-generation zoned power distribution system, the number of IPD channels in each body domain controller unit will increase, leading to an increase in the pin resources of the control MCU and an increase in the computing resources required to protect and monitor each IPD. That will in turn increase the work required for development, and increase the BOM cost due to the higher functionality of MCUs. To solve these problems, the following functions have been added:

(1) Built-in hardware wiring harness smoke emission protection function as a fuse substitute function

(2) IPD status monitoring via SPI communication and various function settings and holding functions

(3) Realization of on-resistance series lineup by changing MOS chip size

## 1. Introduction

In recent years, various attempts have been made to incorporate new technologies in automobiles, including electrification, automated driving, communications, and AI. In particular, a change in E/E architecture is being sought to realize automated driving. E/E architecture is a system structure that connects various components such as ECUs, sensors, and actuators installed in automobiles. E/E stands for Electrical/Electronics, and architecture means system configuration and design concept.

The transformation of E/E architecture has evolved the form of functional aggregation from functionally-distributed to domain-based. Furthermore, the transition to a zoned system is a turning point toward a system in which the onboard computer is assumed to operate the car in place of the driver, in anticipation of automated driving. Conventional power distribution systems use mechanical relays and fuses, but the high failure rate of the contact points, current consumption during operation, and ECU placement restrictions, etc., pose challenges. Therefore, it is expected that a large number of semiconductor switch devices such as IPDs will be used instead of mechanical relays and fuses in zoned E/E architectures.

IPD stands for Intelligent Power Device, which is a semiconductor switch device with built-in additional functions, such as various protection functions. The nextgeneration automotive IPD developed this time is equipped with a hardware-based smoking protection function for harnesses, and provides semiconductor switching functions for various loads by adjusting parameters for each wire diameter and wire type. This feature enables the product to control a large number of IPD channels while reducing the pins and computing resources of the control MCU, thereby increasing its applicability to next-generation zoned E/E architectures.

# 2. Product Overview

This product is a high-side switch IC (IPD) that utilizes our ZeroMOS and BCD processes to achieve low onresistance, high robustness, and advanced control functions. The package is the HSSOP24, a small, high heat-dissipation surface-mount package, which contains two chips, an output element and a control element, in one package.

<sup>\*</sup>Development Section 1, Automotive IC Development Department

Power Device Development Division, Engineering Development Headquarters

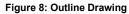

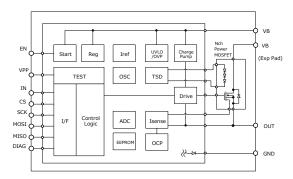

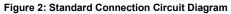

A functional block diagram of the product is shown in Figure 1. A standard connection circuit diagram is shown in Figure 2.

The output element has multiple on-resistance lineups, allowing the selection of an on-resistance product to match the load. In addition, a temperature detection element is built in, enabling detection of overheating conditions at a point close to the heat source.

The control elements include a high-precision current detection circuit, an A/D converter, a CMOS logic control circuit, and a serial communication port. In addition, a harness smoking protection function is provided, which estimates the harness temperature from the load current and shuts off the output before smoke emission develops. Harness parameters can be flexibly set according to smoke emission characteristics, and various setting information can be retained in the internal non-volatile memory (EEPROM).

The product also has intelligent protection functions required for automotive applications, such as overvoltage/ low-voltage protection, overcurrent protection, overheat protection, reverse connection protection, and SPI communication breakdown protection (Limp Home). The operation settings and status of these protection functions can be checked via serial communication.

Figure 1: Functional Block Diagram

## 3. Features

### 3.1. Wiring Harness Protection Function

As a differentiating feature, this product incorporates a harness protection smoke emission function based on hardware harness temperature estimation. This function uses a high-precision arithmetic circuit in the digital circuit to estimate the temperature of the harness from the load current and harness information as appropriate, and performs its protection operation when the preset protective temperature is reached.

Harness information and protective actions can be configured by the customer. Since these settings can be stored in EEPROM, they can be set once and the protection functions can be easily utilized. For harness information, parameters can be set according to the physical characteristics of each harness, in order to accommodate various types of harness. The main parameters that can be set for protective actions are listed below.

INEN: ON/OFF control switching via SPI communication

SR: Output slew rate setting

LHAct: SPI communication breakdown protection (Limp Home) operation setting

#### 3.2. EEPROM (non-volatile memory)

EEPROM is mounted in the product to hold various setting information. The EEPROM can be written and read by the user via SPI communication. The various setting information written in advance is automatically read from EEPROM after power-on, eliminating the need for initial setting of various information via SPI communication. This is expected to shorten the overall system setup time and reduce the load on the ECU.

A humming code is added as an ECC (Error-Correction Code) to the data written to the EEPROM. This code enables error detection and one-bit data correction of transmitted and received data, and is expected to improve the robustness of the entire system.

# 3.3. Evaluation Environment for Operation Verification

A standard evaluation environment was established to support the characterization of the SIP1 Series.

- (1) Evaluation board with 3 channels for our IPD

- (2) Microcontroller board program for communication and IC control

- (3) GUI program for controlling and monitoring ICs

Figure 3 shows the SIP1 Series evaluation board. Combining this evaluation board with a microcontroller board and connecting it to a PC via USB makes it possible to set parameters and monitor the operation of the IPD.

After setting various parameters of the wiring harness and various operation options in the GUI, the output can be controlled by pressing the On/Off button. The IPD successively calculates the estimated harness temperature from the load current and harness parameters, and can monitor the load current, estimated harness temperature, and IPD status information via SPI communication. Figure 4 shows an example of a GUI monitor waveform.

Figure 3: SIP1 Series Evaluation Board

Figure 4: Example GUI Monitor Waveform

## 4. Design

## 4.1. Monolithic IC Chip

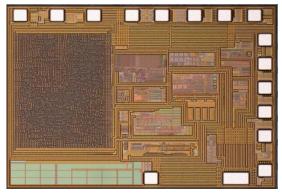

Figure 5 shows a photographic view of the chip surface of a monolithic IC. The process applied is our 8th-generation monolithic IC process, which is a BCD process combining 180nm fine CMOS and 100V voltage tolerance high-voltage DMOS. The BCD process is a process that can integrate bipolar transistors, CMOS, and low on-resistance DMOS FETs on a single chip.

CMOS logic control circuits are designed efficiently using language design (Verilog-HDL). In addition, the failure detection rate of CMOS logic control circuits must be improved to ensure high quality and reliability in automotive applications. This product achieves a high failure detection rate by introducing ATPG (Automatic Test Pattern Generator) and IDDQ testing to chip testing.

Figure 5: Photographic View of Monolithic IC Chip Surface

### 4.2. MOS FET

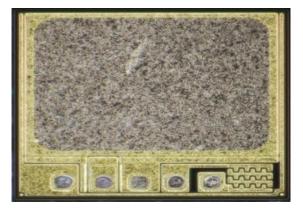

Figure 6 shows a photographic view of a MOS FET surface. The MOS FETs use our Zero MOS process with 40V voltage tolerance. The Zero MOS process has industry-leading FOM (Figure of Merit) performance, resulting in smaller size and lower on-resistance.

In addition, although reducing the wafer thickness of MOS FETs is effective in reducing the on-resistance, this entails risks in transit and risk of damage due to warpage. As a countermeasure, when grinding wafers, a process is employed in which the outermost rim of the wafer is left intact and only the inner periphery is ground to make the wafer thinner.

Figure 6: Photographic View of MOS FET Surface

#### 4.3. Package

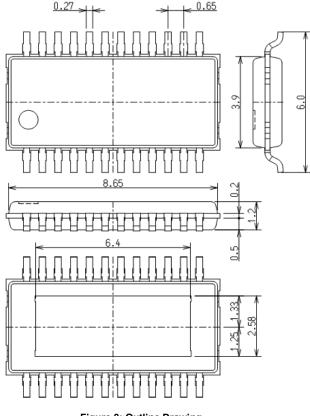

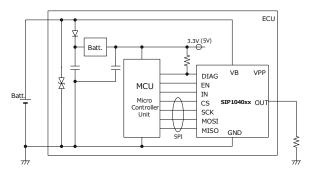

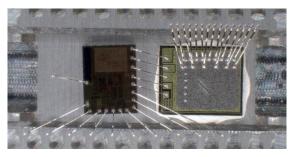

Figure 7 shows the internal structure of the SIP1 Series. An outline drawing is shown in Figure 8.

This product has a structure in which two chips are mounted on a metal frame that serves as a heat dissipation fin. The following on-resistance series lineups are planned, to be produced by changing the MOS FET chip size.

$9.5\mathrm{m}\Omega$ ,  $7.5\mathrm{m}\Omega$ ,  $5.0\mathrm{m}\Omega$ ,  $4.0\mathrm{m}\Omega$ ,  $3.0\mathrm{m}\Omega$ ,  $2.0\mathrm{m}\Omega$ ,

$1.6m\Omega$ ,  $1.3m\Omega$ ,  $1.0m\Omega$

DAF (Die Attach Film) tape is used to connect the monolithic IC chip to the metal frame to ensure insulation, and sintered silver is used to connect the MOS FET chip to the metal frame to ensure high thermal conductivity and reliability. The connection between the chip and the external pins is made by wire bonding.

# 5. Conclusion

As the next-generation IPD for automotive applications, we have developed the SIP1 Series, a next-generation IPD with the following functions, in accordance with the zoned E/E architecture.

- Built-in hardware wiring harness smoke emission protection function as a fuse replacement function

- (ii) IPD status monitoring and various function settings and holding functions via SPI communication

- (iii) Realization of on-resistance series lineup by changing MOS chip size

In the future, we intend to expand the on-resistance lineup, consider further functional enhancements, and develop products that meet user needs.

Figure 7 Internal Structure Diagram