# LLC Current-resonant Off-line Switching Controller SSC3S927A

# **Description**

The SSC3S927A is a controller with SMZ\* method for LLC current resonant switching power supplies, incorporating a floating drive circuit for a high-side power MOSFET. The IC includes useful functions such as the standby function, automatic dead time adjustment, and capacitive mode detection. The IC allows power supply systems to have fewer external components, compactness, high efficiency, low noise, and high cost-effectiveness.

\* SMZ: soft-switched multi-resonant zero current switch, achieving soft switching operation during all switching periods.

#### **Features**

- Pb-free (RoHS compliant)

- Standby Mode Change Function by External Singal

- $^{\circ}$  Output Power at Light Load:  $P_{O} = 150 \text{ mW} (P_{IN} = 0.27 \text{ W})$

- Burst Operation in Standby Mode

- Soft-on/Soft-off Function: Audible Noise Suppression

- Soft-start Function

- Capacitive Mode Detection Function

- Reset Detection Function

- Automatic Dead Time Adjustment Function

- Built-in Startup Circuit

- X-capacitor Discharge Function

- Protections

- Input Voltage Protection

Input High-voltage Protection (HVP): Auto-restart

Input Undervoltage Protection (UVP): Auto-restart

- High-side Driver UVLO: Auto-restart

- Overcurrent Protection (OCP): Auto-restart, Peak

Drain Current Detection, Two Types of Detection

- Overload Protection (OLP): Auto-restart

- Overvoltage Protection (OVP): Auto-restart

- REG Overvoltage Protection (REG\_OVP): Autorestart

- <sup>n</sup> Thermal Shutdown (TSD): Auto-restart

# **Package**

SOP18

Not to scale

# **Applications**

Switching power supplies for electronic devices such as:

- Digital Appliances (e.g., Television)

- Office Automation (OA) Equipment (e.g., Server, Multi-function Printer)

- Industrial Apparatus

- Communication Facilities

# **Typical Application**

# **Contents**

| Description                                                                     | 1          |

|---------------------------------------------------------------------------------|------------|

| Contents                                                                        | 2          |

| 1. Absolute Maximum Ratings                                                     | 3          |

| 2. Electrical Characteristics                                                   | 4          |

| 3. Mechanical Characteristic                                                    |            |

| 4. Block Diagram                                                                |            |

| <u> </u>                                                                        |            |

| 5. Pin Configuration Definitions                                                |            |

| 6. Typical Application                                                          | 8          |

| 7. Physical Dimensions                                                          | 9          |

| 8. Marking Diagram                                                              | 9          |

| 9. Operational Description                                                      | 10         |

| 9.1 Resonant Circuit Operation                                                  | 10         |

| 9.2 Startup Operation                                                           | 13         |

| 9.3 Undervoltage Lockout (UVLO)                                                 | 13         |

| 9.4 Bias Assist Function                                                        |            |

| 9.5 Soft-start Function                                                         |            |

| 9.6 Minimum and Maximum Switching Frequency Setting                             |            |

| 9.7 High-side Driver                                                            |            |

| 9.8 Constant Voltage Control Operation 9.9 Standby Function                     | - 15<br>15 |

|                                                                                 |            |

| 9.9.1 Standby Mode Switched by External Signal9.9.2 Burst Oscillation Operation | - 15<br>17 |

| 9.10 Automatic Dead Time Adjustment Function                                    | - 1/<br>17 |

| 9.11 Capacitive Mode Detection Function                                         | 17<br>18   |

| 9.12 X-Capacitor Discharge Function                                             | 19         |

| 9.13 Reset Detection Function                                                   | 20         |

| 9.14 Overvoltage Protection (OVP)                                               | - 23       |

| 9.15 REG Overvoltage Protection (REG_OVP)                                       | - 23       |

| 9.16 Input Voltage Protection                                                   | - 23       |

| 9.16.1 Input High-voltage Protection (HVP)                                      | 23         |

| 9.16.2 Input Undervoltage Protection (UVP)                                      |            |

| 9.17 Overcurrent Protection (OCP)                                               |            |

| 9.18 Overload Protection (OLP)                                                  | 25         |

| 9.19 Thermal Shutdown (TSD)                                                     | 26         |

| 10. Design Notes                                                                |            |

| 10.1 External Components                                                        |            |

| 10.1.1 Input and output electrolytic capacitors                                 | 26         |

| 10.1.2 Resonant transformer                                                     |            |

| 10.1.3 Current detection resistor, R <sub>OCP</sub>                             | 26         |

| 10.1.4 Current resonant capacitor, Ci                                           | 26         |

| 10.1.5 Gate Pin Peripheral Circuit                                              |            |

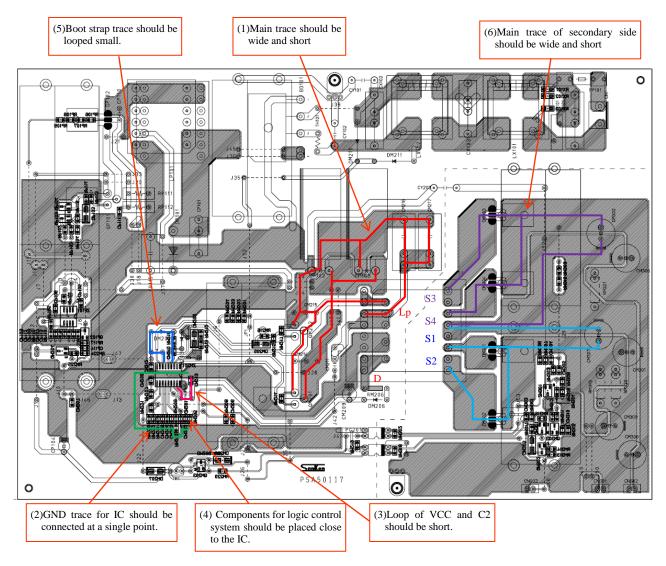

| 10.2 PCB Trace Layout and Component Placement                                   |            |

| 11. Pattern Layout Example                                                      | 28         |

| Important Notes                                                                 | 30         |

# **SSC3S927A**

# 1. Absolute Maximum Ratings

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); and current coming out of the IC (sourcing) is negative current (-).

Unless otherwise specified, T<sub>A</sub> is 25°C.

| Parameter                         | Symbol              | Pins    | Rating                     | Unit |

|-----------------------------------|---------------------|---------|----------------------------|------|

| VSEN Pin Sink Current             | $I_{SEN}$           | 1 – 10  | 1.0                        | mA   |

| Control Part Input Voltage        | V <sub>CC</sub>     | 2 – 10  | -0.3 to 35                 | V    |

| FB Pin Voltage                    | $V_{\mathrm{FB}}$   | 3 – 10  | -0.3 to 6                  | V    |

| SB Pin Voltage                    | $V_{SB}$            | 4 - 10  | -0.3 to 6                  | V    |

| CSS Pin Voltage                   | V <sub>CSS</sub>    | 5 – 10  | -0.3 to 6                  | V    |

| CL Pin Voltage                    | $V_{\mathrm{CL}}$   | 6 – 10  | -0.3 to 6                  | V    |

| RC Pin Voltage                    | $V_{RC}$            | 7 – 10  | -6 to 6                    | V    |

| CD Pin Voltage                    | $V_{CD}$            | 8 – 10  | -0.3 to 6                  | V    |

| MODE Pin Voltage                  | $V_{\mathrm{MODE}}$ | 9 – 10  | -0.3 to 6                  | V    |

| VGL pin Voltage                   | $V_{ m GL}$         | 11 – 10 | $-0.3$ to $V_{REG} + 0.3$  | V    |

| REG pin Source Current            | $I_{REG}$           | 12 – 10 | -10.0                      | mA   |

| Voltage Between VB Pin and VS Pin | $V_B-V_S$           | 14 – 15 | -0.3 to 20.0               | V    |

| VS Pin Voltage                    | Vs                  | 15 – 10 | -1 to 600                  | V    |

| VGH Pin Voltage                   | $V_{ m GH}$         | 16 – 10 | $V_S - 0.3$ to $V_B + 0.3$ | V    |

| ST Pin Voltage                    | V <sub>ST</sub>     | 18 – 10 | -0.3 to 600                | V    |

| Operating Ambient Temperature     | Тор                 |         | -40 to 85                  | °C   |

| Storage Temperature               | Tstg                |         | -40 to 125                 | °C   |

| Junction Temperature              | $T_{\mathrm{J}}$    | _       | 150                        | °C   |

# 2. Electrical Characteristics

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); and current coming out of the IC (sourcing) is negative current (-).

Unless otherwise specified, T<sub>A</sub> is 25 °C, V<sub>CC</sub> is 19 V.

| Unless otherwise specified, T <sub>A</sub> is 25 °C,          |                                   | 1                              | <del>                                     </del> |      |      | ı    |      |  |  |

|---------------------------------------------------------------|-----------------------------------|--------------------------------|--------------------------------------------------|------|------|------|------|--|--|

| Parameter                                                     | Symbol                            | Conditions                     | Pins                                             | Min. | Typ. | Max. | Unit |  |  |

| Start Circuit and Circuit Current                             | Start Circuit and Circuit Current |                                |                                                  |      |      |      |      |  |  |

| Operation Start Voltage                                       | $V_{\text{CC(ON)}}$               |                                | 2 – 10                                           | 15.8 | 17.0 | 18.2 | V    |  |  |

| Operation Stop Voltage (1)                                    | V <sub>CC(OFF)</sub>              |                                | 2 – 10                                           | 7.8  | 8.9  | 9.8  | V    |  |  |

| Startup Current Biasing Threshold Voltage <sup>(1)</sup>      | V <sub>CC(BIAS)</sub>             |                                | 2 – 10                                           | 9.0  | 9.8  | 10.6 | V    |  |  |

| Circuit Current in Operation                                  | I <sub>CC(ON)</sub>               |                                | 2 – 10                                           | _    | _    | 10.0 | mA   |  |  |

| Circuit Current in Non-Operation (2)                          | I <sub>CC(OFF)</sub>              | $V_{CC} = 11 \text{ V}$        | 2 – 10                                           | _    | 0.7  | 1.5  | mA   |  |  |

| Startup Current (2)                                           | Ist                               |                                | 18 – 10                                          | 3.0  | 6.0  | 9.0  | mA   |  |  |

| Protection Operation Release Threshold Voltage <sup>(1)</sup> | V <sub>CC(P.OFF)</sub>            |                                | 2 – 10                                           | 7.8  | 8.9  | 9.8  | V    |  |  |

| Circuit Current in Protection                                 | $I_{CC(P)}$                       | $V_{CC} = 10 \text{ V}$        | 2 – 10                                           | _    | 0.7  | 1.5  | mA   |  |  |

| Oscillator                                                    |                                   |                                |                                                  |      |      |      |      |  |  |

| Minimum Frequency                                             | f <sub>(MIN)</sub>                |                                | 11 – 10<br>16 – 15                               | 27.5 | 31.5 | 35.5 | kHz  |  |  |

| Maximum Frequency                                             | f <sub>(MAX)</sub>                |                                | 11 – 10<br>16 – 15                               | 230  | 300  | 380  | kHz  |  |  |

| Minimum Dead-Time                                             | t <sub>d(MIN)</sub>               |                                | 11 – 10<br>16 – 15                               | 0.04 | 0.24 | 0.44 | μs   |  |  |

| Maximum Dead-Time                                             | $t_{d(MAX)}$                      |                                | 11 - 10 $16 - 15$                                | 1.20 | 1.65 | 2.20 | μs   |  |  |

| Externally Adjusted Minimum Frequency 1                       | f <sub>(MIN)</sub> ADJ1           | $R_{CSS} = 30 \text{ k}\Omega$ | 11 – 10<br>16 – 15                               | 69   | 73   | 77   | kHz  |  |  |

| Externally Adjusted Minimum Frequency 2                       | $f_{(MIN)ADJ2}$                   | $R_{CSS} = 77 \text{ k}\Omega$ | 11 – 10<br>16 – 15                               | 42.4 | 45.4 | 48.4 | kHz  |  |  |

| Feedback Control                                              |                                   |                                |                                                  |      |      |      |      |  |  |

| FB Pin Oscillation Start Threshold Voltage                    | V <sub>FB(ON)</sub>               |                                | 3 – 10                                           | 0.15 | 0.30 | 0.45 | V    |  |  |

| FB Pin Oscillation Stop Threshold Voltage                     | $V_{FB(OFF)} \\$                  |                                | 3 – 10                                           | 0.05 | 0.20 | 0.35 | V    |  |  |

| FB Pin Maximum Source Current                                 | I <sub>FB(MAX)</sub>              | $V_{FB} = 0 V$                 | 3 – 10                                           | -300 | -195 | -100 | μA   |  |  |

| FB Pin Reset Current                                          | I <sub>FB(R)</sub>                |                                | 3 – 10                                           | 2.5  | 5.0  | 7.5  | mA   |  |  |

| Soft-start                                                    |                                   |                                |                                                  |      |      |      |      |  |  |

| CSS Pin Charging Current                                      | I <sub>CSS(C)</sub>               |                                | 5 – 10                                           | -120 | -105 | -90  | μΑ   |  |  |

| CSS Pin Reset Current                                         | I <sub>CSS(R)</sub>               | $V_{CC} = 11V$                 | 5 – 10                                           | 1.1  | 1.8  | 2.5  | mA   |  |  |

| Maximum Frequency in Soft-start                               | f <sub>(MAX)SS</sub>              |                                | 11 – 10<br>16 – 15                               | 400  | 500  | 600  | kHz  |  |  |

| Standby                                                       |                                   |                                |                                                  |      |      |      |      |  |  |

| MODE Pin Standby Release Threshold<br>Voltage                 | V <sub>MODE(NRM)</sub>            |                                | 9 – 10                                           | 0.2  | 0.3  | 0.4  | V    |  |  |

| MODE Pin Standby Threshold Voltage                            | V <sub>MODE(STB)</sub>            |                                | 9 – 10                                           | 0.4  | 0.5  | 0.6  | V    |  |  |

| MODE Pin Source Current                                       | Imode(src)                        |                                | 9 – 10                                           | -7.5 | -5.0 | -2.5 | μA   |  |  |

| MODE Pin Clamp Voltage                                        | V <sub>MODE(CLA</sub>             |                                | 9 – 10                                           | 0.6  | 0.7  | 0.8  | V    |  |  |

|                                                               |                                   |                                |                                                  |      |      |      |      |  |  |

$<sup>^{(1)}\</sup> V_{CC(OFF)} = V_{CC(P.OFF)} < V_{CC(BIAS)}\ always.$

$<sup>^{(2)}</sup>$   $I_{START}$  =  $I_{ST}$  –  $I_{CC(OFF)},$  where  $I_{START}$  is VCC pin source current in startup.

# **SSC3S927A**

| Parameter                                             | Symbol                  | Conditions                      | Pins               | Min.  | Тур.                          | Max.  | Unit |

|-------------------------------------------------------|-------------------------|---------------------------------|--------------------|-------|-------------------------------|-------|------|

| SB Pin Standby Threshold Voltage                      | V <sub>SB(STB)</sub>    |                                 | 4 – 10             | _     | $V_{\text{MODE}} \times 0.95$ | _     | V    |

| 55 Thi Standoy Threshold Voluge                       | V 3D(31D)               | V <sub>MODE</sub> = 3 V         | 4 – 10             | 2.67  | 2.85                          | 2.97  | V    |

| SB Pin Oscillation Start Threshold                    | V <sub>SB(ON)</sub>     |                                 | 4 – 10             |       | $V_{\text{MODE}} \times 0.55$ |       | V    |

| Voltage                                               |                         | $V_{\text{MODE}} = 3 \text{ V}$ | 4 – 10             | 1.47  | 1.65                          | 1.77  | V    |

| SB Pin Oscillation Stop Threshold Voltage             | V <sub>SB(OFF)</sub>    |                                 | 4 – 10             | —     | $V_{\text{MODE}} \times 0.50$ | _     | V    |

|                                                       |                         | $V_{\text{MODE}} = 3 \text{ V}$ | 4 – 10             | 1.32  | 1.50                          | 1.62  | V    |

| SB Pin Oscillation Clamp Voltage                      | V <sub>SB(CLAMP)</sub>  |                                 | 4 – 10             | _     | $V_{\text{MODE}} \times 0.45$ | _     | V    |

|                                                       |                         | $V_{\text{MODE}} = 3 \text{ V}$ | 4 – 10             |       | 1.35                          | _     | V    |

| SB Pin Source Current (High)                          | I <sub>SB(SRC)H</sub>   |                                 | 4 – 10             | -19   | -15                           | -11   | μA   |

| SB Pin Source Current (Low)                           | I <sub>SB(SRC)L</sub>   |                                 | 4 – 10             | -7.5  | -5.0                          | -2.5  | μA   |

| SB Pin Sink Current (High)                            | I <sub>SB(SNK)H</sub>   |                                 | 4 – 10             | 11    | 15                            | 19    | μA   |

| SB Pin Sink Current (Low)                             | I <sub>SB(SNK)L</sub>   |                                 | 4 – 10             | 2.5   | 5.0                           | 7.5   | μΑ   |

| Overload Protection (OLP)                             |                         |                                 |                    |       |                               |       |      |

| RC Pin Threshold Voltage (Low)                        | V <sub>RC(L)</sub>      |                                 | 7 – 10             | 1.80  | 1.90                          | 2.00  | V    |

| RC FIII Tilleshold Voltage (Low)                      | V RC(L)                 |                                 | 7 – 10             | -2.00 | -1.90                         | -1.80 | V    |

| CL pin OLP Threshold Voltage                          | V <sub>CL(OLP)</sub>    |                                 | 6 – 10             | 3.9   | 4.2                           | 4.5   | V    |

| CL Pin Source Current 1                               | I <sub>CL(SRC)1</sub>   |                                 | 6 – 10             | -29   | -17                           | -5    | μΑ   |

| CL Pin Source Current 2                               | I <sub>CL(SRC)2</sub>   |                                 | 6 – 10             | -180  | -135                          | -90   | μΑ   |

| CL Pin Sink Current                                   | I <sub>CL(SNK)</sub>    |                                 | 6 – 10             | 10    | 30                            | 50    | μΑ   |

| Input Undervoltage Protection (UVP)                   |                         |                                 |                    |       |                               |       |      |

| VSEN Pin Threshold Voltage (On)                       | V <sub>SEN(ON)</sub>    |                                 | 1 – 10             | 1.150 | 1.200                         | 1.250 | V    |

| VSEN Pin Threshold Voltage (Off) 1                    | V <sub>SEN(OFF)1</sub>  |                                 | 1 – 10             | 0.955 | 1.000                         | 1.045 | V    |

| VSEN Pin Threshold Voltage (Off) 2                    | V <sub>SEN(OFF)2</sub>  |                                 | 1 – 10             | _     | 0.8                           |       | V    |

| VSEN Pin HVP Threshold Voltage                        | V <sub>SEN(HVP)</sub>   |                                 | 1 – 10             | 5.3   | 5.6                           | 5.9   | V    |

| VSEN Pin Clamp Voltage                                | V <sub>SEN(CLAMP)</sub> |                                 | 1 – 10             | 6.0   | _                             |       | V    |

| VSEN pin Threshold Voltage for AC Line<br>Detection 1 | V <sub>SEN(AC)1</sub>   |                                 | 1 – 10             | 2.56  | 2.70                          | 2.84  | V    |

| VSEN Pin Threshold Voltage for AC Line Detection 2    | V <sub>SEN(AC)2</sub>   |                                 | 1 – 10             |       | 2.4                           | _     | V    |

| CD Pin Threshold Voltage 1                            | $V_{CD1}$               |                                 | 8 – 10             | 2.8   | 3.0                           | 3.2   | V    |

| CD Pin Source Current                                 | I <sub>CD(SRC)</sub>    | $V_{CD} = 0 V$                  | 8 – 10             | -12.0 | -10.2                         | -8.5  | μΑ   |

| CD Pin Reset Current                                  | $I_{CD(R)}$             | $V_{CD} = 2 V$                  | 8 – 10             | 1.0   | 2.5                           | 4.0   | mA   |

| Reset Detection                                       |                         |                                 |                    |       |                               |       |      |

| Maximum Reset Time                                    | t <sub>RST(MAX)</sub>   |                                 | 11 – 10<br>16 – 15 | 12.5  | 15.7                          | 18.9  | μs   |

| <b>Driver Circuit Power Supply</b>                    |                         |                                 |                    |       |                               |       |      |

| VREG Pin Output Voltage                               | $V_{REG}$               |                                 | 12 – 10            | 9.6   | 10.0                          | 10.8  | V    |

| High-side Driver                                      | •                       | •                               | -                  | -     |                               |       |      |

| High-side Driver Operation Start Voltage              | V <sub>BUV(ON)</sub>    |                                 | 14 – 15            | 5.7   | 6.8                           | 7.9   | V    |

| High-side Driver Operation Stop Voltage               | V <sub>BUV(OFF)</sub>   |                                 | 14 – 15            | 5.5   | 6.4                           | 7.3   | V    |

# **SSC3S927A**

| Parameter                              | Symbol                                         | Conditions                                                                                                           | Pins               | Min.  | Тур.  | Max.  | Unit |

|----------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------|-------|-------|-------|------|

| Driver Circuit                         |                                                |                                                                                                                      |                    |       |       |       |      |

| VGL,VGH Pin Source Current 1           | I <sub>GL(SRC)1</sub><br>I <sub>GH(SRC)1</sub> | $\begin{aligned} V_{REG} &= 10.5 \ V \\ V_{B} &= 10.5 \ V \\ V_{GL} &= 0 \ V \\ V_{GH} &= 0 \ V \end{aligned}$       | 11 – 10<br>16 – 15 |       | -540  | _     | mA   |

| VGL,VGH Pin Sink Current 1             | I <sub>GL(SNK)1</sub> I <sub>GH(SNK)1</sub>    | $\begin{aligned} &V_{REG} = 10.5 \ V \\ &V_{B} = 10.5 \ V \\ &V_{GL} = 10.5 \ V \\ &V_{GH} = 10.5 \ V \end{aligned}$ | 11 – 10<br>16 – 15 |       | 1.50  | _     | A    |

| VGL,VGH Pin Source Current 2           | Igl(src)2<br>Igh(src)2                         | $\begin{aligned} &V_{REG} = 11.5 \ V \\ &V_{B} = 11.5 \ V \\ &V_{GL} = 10 \ V \\ &V_{GH} = 10 \ V \end{aligned}$     | 11 – 10<br>16 – 15 | -140  | -90   | -40   | mA   |

| VGL,VGH Pin Sink Current 2             | I <sub>GL(SNK)2</sub> I <sub>GH(SNK)2</sub>    | $V_{REG} = 12 \text{ V} V_{B} = 12 \text{ V} V_{GL} = 1.5 \text{ V} V_{GH} = 1.5 \text{ V}$                          | 11 – 10<br>16 – 15 | 140   | 230   | 360   | mA   |

| Capacitive Mode Detection and Overcur  | rent Protecti                                  | on (OCP)                                                                                                             |                    |       |       |       |      |

| Considius Mada Datastian Waltons 1     | V <sub>RC1</sub>                               | 7 – 10                                                                                                               | 0.02               | 0.10  | 0.18  | V     |      |

| Capacitive Mode Detection Voltage 1    |                                                |                                                                                                                      | 7 – 10             | -0.18 | -0.10 | -0.02 | V    |

| Capacitive Mode Detection Voltage 2    | V <sub>RC2</sub>                               |                                                                                                                      | 7 – 10             | 0.35  | 0.50  | 0.65  | V    |

| Capacitive Mode Detection Voltage 2    |                                                |                                                                                                                      |                    | -0.65 | -0.50 | -0.35 | V    |

| RC Pin Threshold Voltage (High)        | V <sub>RC(H)</sub>                             |                                                                                                                      | 7 – 10             | 2.62  | 2.80  | 2.98  | V    |

| Re I III Threshold Voltage (Tright)    | V KC(H)                                        |                                                                                                                      | 7 – 10             | -2.98 | -2.80 | -2.62 | V    |

| CSS Pin Sink Current (Low)             | Icss(L)                                        |                                                                                                                      | 5 – 10             | 1.1   | 1.8   | 2.5   | mA   |

| CSS Pin Sink Current (High)            | Icss(H)                                        |                                                                                                                      | 5 – 10             | 13.0  | 20.5  | 28.0  | mA   |

| Overvoltage Protection (OVP)           |                                                |                                                                                                                      |                    |       |       |       |      |

| VCC Pin OVP Threshold Voltage          | V <sub>CC(OVP)</sub>                           |                                                                                                                      | 2 – 10             | 30.0  | 32.0  | 34.0  | V    |

| REG Pin OVP Threshold Voltage          | V <sub>REG(OVP)</sub>                          |                                                                                                                      | 12 – 10            | 11.5  | 12.4  | 13.5  | V    |

| Thermal Shutdown (TSD)                 |                                                |                                                                                                                      |                    |       |       |       |      |

| Thermal Shutdown Temperature           | T <sub>J(TSD)</sub>                            |                                                                                                                      |                    | 140   | _     | _     | °C   |

| Thermal Characteristic                 |                                                |                                                                                                                      |                    |       |       |       |      |

| Junction to Ambient Thermal Resistance | $\theta_{	extsf{J-A}}$                         |                                                                                                                      |                    | —     |       | 95    | °C/W |

#### **Mechanical Characteristic 3.**

| Parameter      | Conditions | Min. | Typ. | Max. | Unit |

|----------------|------------|------|------|------|------|

| Package Weight |            |      | 0.27 |      | g    |

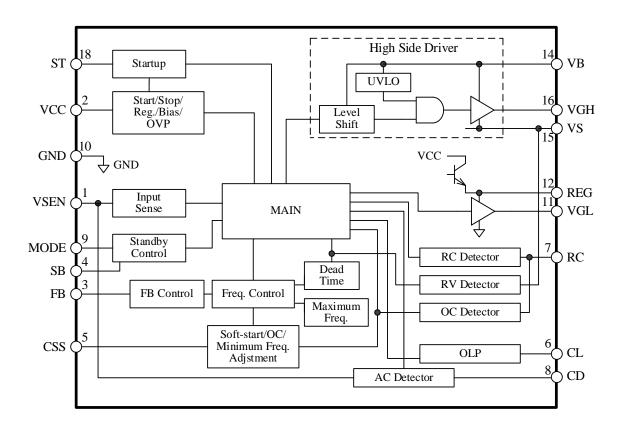

# 4. Block Diagram

# 5. Pin Configuration Definitions

| 1 | O<br>VSEN | ST  | 18 |

|---|-----------|-----|----|

| 2 | VCC       |     |    |

| 3 | FB V      | /GH | 16 |

| 4 | SB        | VS  | 15 |

| 5 | CSS       | VB  | 14 |

| 6 | CL        |     |    |

| 7 | RC I      | REG | 12 |

| 8 | CD V      | VGL | 11 |

| 9 | MODE C    | GND | 10 |

|   |           |     |    |

|        |      | T                                                      |

|--------|------|--------------------------------------------------------|

| Number | Name | Function                                               |

| 1      | VSEN | The mains input voltage detection signal input         |

| 2      | VCC  | Supply voltage input for the IC, and OVP signal input  |

| 3      | FB   | Feedback signal input for constant voltage control     |

| 4      | SB   | Standby control capacitor connection                   |

| 5      | CSS  | Soft-start capacitor connection                        |

| 6      | CL   | Capacitor connection for overload detection            |

| 7      | RC   | Resonant current detection signal input, OCP           |

| /      | KC   | detection signal input, and OLP detection signal input |

| 8      | CD   | Delay time setting capacitor connection                |

| 9      | MODE | Standby mode change signal input                       |

| 10     | GND  | Ground                                                 |

| 11     | VGL  | Low-side gate drive output                             |

| 12     | REG  | Supply voltage output for gate drive circuit           |

| 13     | _    | (Pin removed)                                          |

| 14     | VB   | Supply voltage input for high-side driver              |

| 15     | VS   | Floating ground for high-side driver                   |

| 16     | VGH  | High-side gate drive output                            |

| 17     |      | (Pin removed)                                          |

| 18     | ST   | Startup current input                                  |

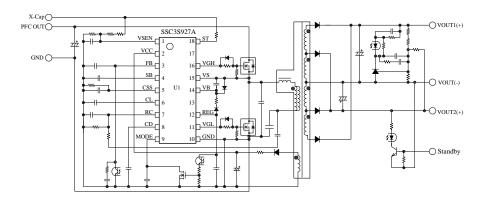

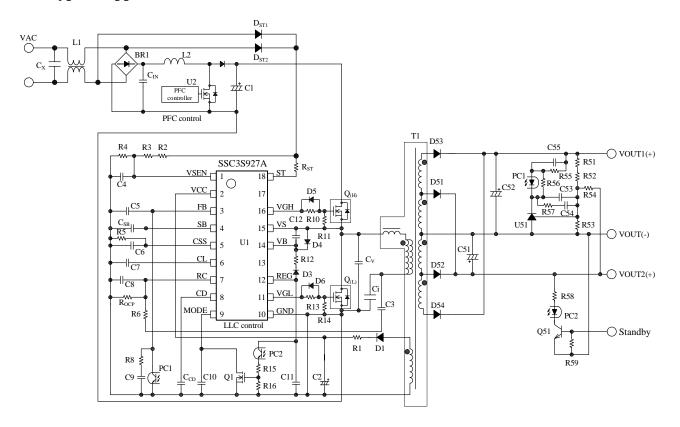

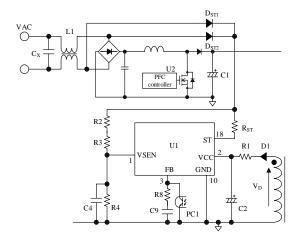

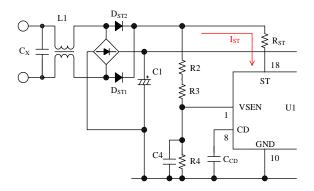

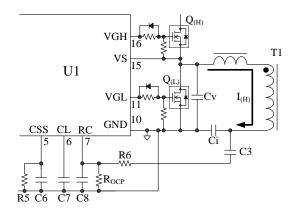

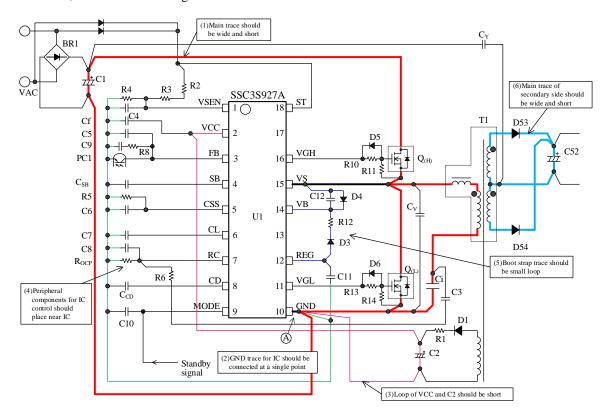

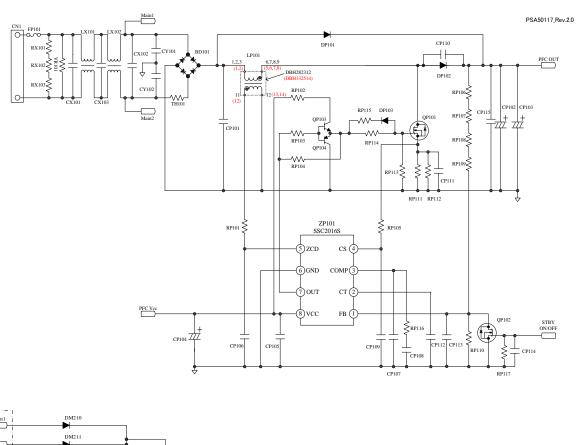

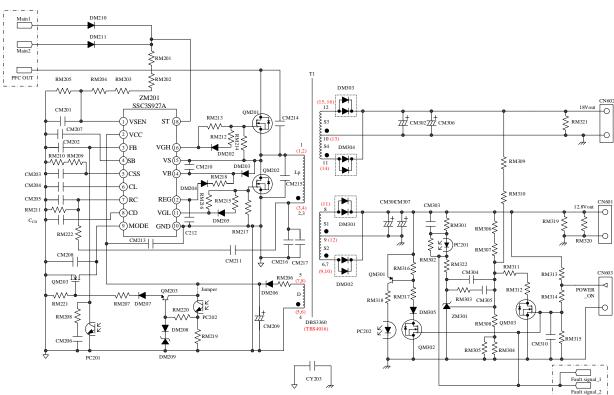

# 6. Typical Application

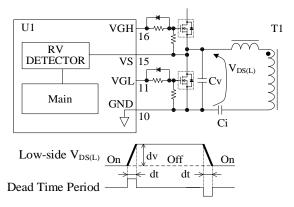

Figure 6-1. Typical Application

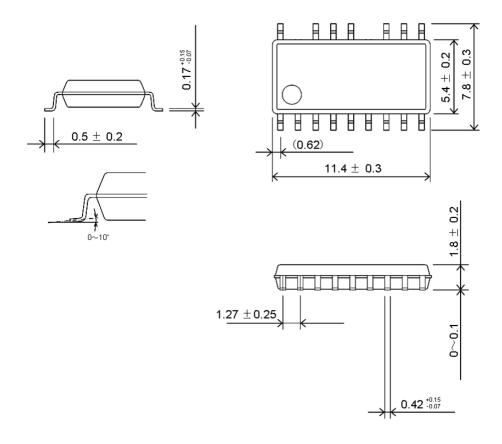

# 7. Physical Dimensions

• SOP18

#### **NOTES:**

- All dimensions in millimeters.

- Pb-free (RoHS compliant)

- $\bullet$  When soldering the products, it is required to minimize the working time within the following limits: Flow: 260 °C / 10 s, 1 time

Soldering Iron: 350 °C / 3.5 s, 1 time

Soldering should be at a distance of at least 1.5 mm from the body of the product.

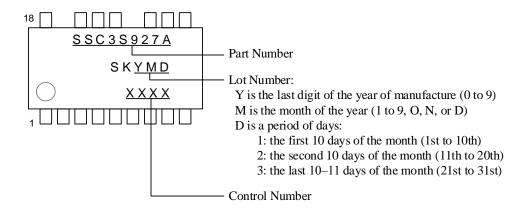

# 8. Marking Diagram

# 9. Operational Description

All of the parameter values used in these descriptions are typical values, unless they are specified as minimum or maximum. Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); and current coming out of the IC (sourcing) is negative current (–).  $Q_{(H)}$  and  $Q_{(L)}$  indicate a high-side power MOSFET and a low-side power MOSFET respectively. Ci and  $C_V$  indicate a current resonant capacitor and a voltage resonant capacitor, respectively.

# 9.1 Resonant Circuit Operation

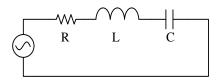

Figure 9-1 shows a basic RLC series resonant circuit. The impedance of the circuit,  $\dot{Z}$ , is as the following Equation.

$$\dot{Z} = R + j\left(\omega L - \frac{1}{\omega C}\right),\tag{1}$$

where  $\omega$  is angular frequency; and  $\omega = 2\pi f$ . Thus,

$$\dot{Z} = R + j \left( 2\pi f L - \frac{1}{2\pi f C} \right). \tag{2}$$

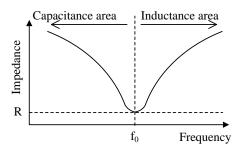

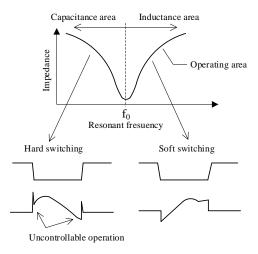

When the frequency, f, changes, the impedance of resonant circuit will change as shown in Figure 9-2.

Figure 9-1. RLC Series Resonant Circuit

Figure 9-2. Impedance of Resonant Circuit

When  $2\pi fL = 1/2\pi fC$ ,  $\dot{Z}$  of Equation (2) becomes the minimum value, R (see Figure 9-2). In the case,  $\omega$  is calculated by Equation (3).

$$\omega = 2\pi f = \frac{1}{\sqrt{I.C}} \tag{3}$$

The frequency in which  $\dot{Z}$  becomes a minimum value is called the resonant frequency,  $f_0$ . The impedance of a resonant circuit has two areas: an inductive area at frequencies higher than  $f_0$ , and a capacitive area at frequencies lower than  $f_0$ .

From Equation (3),  $f_0$  is as follows:

$$f_0 = \frac{1}{2\pi\sqrt{LC}}. (4)$$

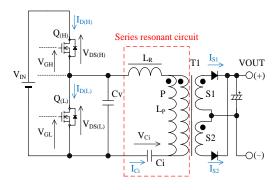

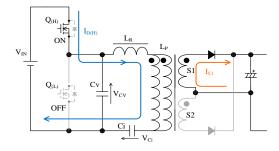

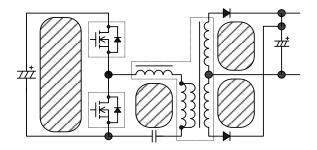

Figure 9-3 shows the circuit of a current resonant power supply. The basic configuration of the current resonant power supply is a half-bridge converter. The switching devices,  $Q_{(H)}$  and  $Q_{(L)}$ , are connected in series with V<sub>IN</sub>. The series resonant circuit and the voltage resonant capacitor, C<sub>V</sub>, are connected in parallel with Q<sub>(L)</sub>. The series resonant circuit consists of the following components: the resonant inductor, L<sub>R</sub>; the primary winding, P, of a transformer, T1; and the current resonant capacitor, Ci. The coupling between the primary and secondary windings of T1 is designed to be poor so that the leakage inductance increases. This leakage inductance is used for L<sub>R</sub>. This results in a downsized series resonant circuit. The dotted mark with T1 describes the winding polarity. The secondary windings, S1 and S2, are connected so that the polarities are set to the same direction as shown in Figure 9-3. In addition, the winding numbers of each other should be equal. From Equation (1), the impedance of a current resonant power supply is calculated by Equation (5). From Equation (4), the resonant frequency,  $f_0$ , is calculated by Equation (6).

$$\dot{Z} = R + j \left\{ \omega (L_R + L_P) - \frac{1}{\omega Ci} \right\}, \tag{5}$$

$$f_0 = \frac{1}{2\pi\sqrt{(L_R + L_P) \times Ci}},\tag{6}$$

where:

R is the equivalent resistance of load,  $L_R$  is the inductance of the resonant inductor,  $L_P$  is the inductance of the primary winding P, and Ci is the capacitance of current resonant capacitor.

Figure 9-3. Current Resonant Power Supply Circuit

In the current resonant power supply,  $Q_{(H)}$  and  $Q_{(L)}$  are alternatively turned on and off. The on and off times of them are equal. There is a dead time between the on periods of  $Q_{(H)}$  and  $Q_{(L)}$ . During the dead time,  $Q_{(H)}$  and  $Q_{(L)}$  are in off status.

The current resonant power supply controls frequencies to maintain the output voltage at a constant level. When the output voltage decreases, the IC decreases the switching frequency so that the output power is increased to keep a constant output voltage. This must be controlled in the inductance area ( $f_{SW}$  <  $f_0$ ). Since the winding current is delayed from the winding voltage in the inductance area, the turn-on operates in a ZCS (Zero Current Switching); and the turn-off operates in a ZVS (Zero Voltage Switching). Thus, the switching losses of  $Q_{(H)}$  and  $Q_{(L)}$  are nearly zero. In the capacitance area ( $f_{SW} < f_0$ ), the current resonant power supply operates as follows: When the output voltage decreases, the switching frequency is decreased; and then, the output power is further decreased. Therefore, the output voltage cannot be kept constant. Since the winding current phase advances ahead of the winding voltage in the capacitance area, Q<sub>(H)</sub> and Q<sub>(L)</sub> operate in the hard switching. This results in the increases of a power loss. This operation in the capacitance area is called the capacitive mode operation. The current resonant power supply must be operated without the capacitive mode operation (for more details, see Section 9.11).

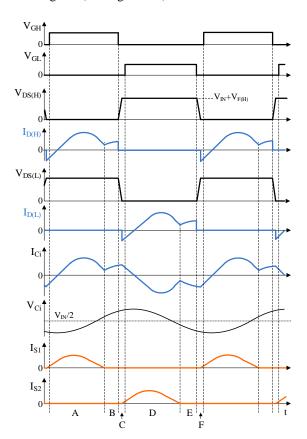

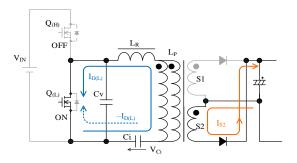

Figure 9-4 describes the basic operation waveform of current resonant power supply (see Figure 9-3 for the symbols in Figure 9-4). For the description of current resonant waveforms in normal operation, the operation is separated into a period A to F. In the following description:

$$\begin{split} &I_{D(H)} \text{ is the current of } Q_{(H)}, \\ &I_{D(L)} \text{ is the current of } Q_{(L)}, \\ &V_{F(H)} \text{ is the forwerd voltage of } Q_{(H)}, \\ &V_{F(L)} \text{ is the forwerd voltage of } Q_{(L)}, \\ &I_{L} \text{ is the current of } L_{R}, \\ &V_{IN} \text{ is the input voltage}, \\ &V_{Ci} \text{ is Ci voltage, and} \\ &V_{CV} \text{ is } C_{V} \text{ voltage.} \end{split}$$

The current resonant power supply operations in period A to F are as follows:

#### 1) Period A

When  $Q_{(H)}$  is on, energy is stored in the series resonant circuit by  $I_{D(H)}$  that flows through the resonant circuit and the transformer (see Figure 9-5). At the same time, the energy is transferred to the secondary circuit. When the primary winding of the transformer can no longer maintain the voltage sufficient to turn on the secondary-side diode, the energy transfer to the secondary-side ends.

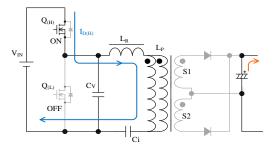

2) Period B

After the secondary-side current becomes zero, the resonant current flows through only the primary side to charge Ci (see Figure 9-6).

Figure 9-4. The Basic Operation Waveforms of Current Resonant Power Supply

Figure 9-5. Operation in period A

Figure 9-6. Operation in Period B

© SANKEN ELECTRIC CO., LTD. 2024

#### 3) Period C

C is the dead-time period.  $Q_{(H)}$  and  $Q_{(L)}$  are in off status. When  $Q_{(H)}$  turns off,  $C_V$  is discharged with  $I_L$  that is supplied by the energy stored in the series resonant circuit applies (see Figure 9-7). When  $V_{CV}$  decreases to  $-V_{F(L)}$ ,  $-I_{D(L)}$  flows through the body diode of  $Q_{(L)}$ ; and  $V_{CV}$  is clamped to  $-V_{F(L)}$ . After that,  $Q_{(L)}$  turns on. Since  $V_{DS(L)}$  is nearly zero at this point,  $Q_{(L)}$  operates in the ZVS and the ZCS, resuling in almost no switching loss.

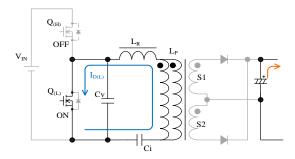

#### 4) Period D

Immidiately after  $Q_{(L)}$  turns on,  $-I_{D(L)}$ , which was flowing in Period C, continues to flow through  $Q_{(L)}$  for a while. Then,  $I_{D(L)}$  flows as shown in Figure 9-8; and  $V_{Ci}$  is applied to the primary winding voltage of the transformer. At the same time, energy is transferred to the secondary circuit. When the primary winding of the transformer can no longer maintain the voltage sufficient to turn on the secondary-side diode, the energy transfer to the secondary-side ends.

#### 5) Period E

After the secondary-side current becomes zero, the resonant current flows through only the primary side to charge Ci (see Figure 9-9).

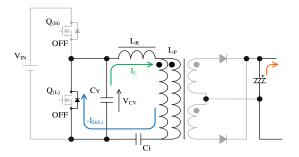

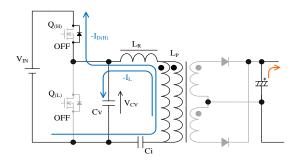

#### 6) Period F

F is the dead-time period.  $Q_{(H)}$  and  $Q_{(L)}$  are in off status.

When  $Q_{(L)}$  turns off,  $C_V$  is charged with  $-I_L$  that is supplied by the energy stored in the series resonant circuit applies (see Figure 9-10). When  $V_{CV}$  reaches  $V_{IN} + V_{F(H)}$ ,  $-I_{D(H)}$  flows through body diode of  $Q_{(H)}$ ; and  $V_{CV}$  is clamped to  $V_{IN} + V_{F(H)}$ . After that,  $Q_{(H)}$  turns on. Since  $V_{DS(H)}$  is nearly zero at this point,  $Q_{(H)}$  operates in the ZVS and the ZCS, resulting in almost no switching loss.

#### 7) After the period F

Immidiately after  $Q_{(H)}$  turns on,  $-I_{D(H)}$ , which was flowing in Period F, continues to flow through  $Q_{(H)}$  for a while. Then,  $I_{D(H)}$  flows again; and the operation returns to the period A. The above operation is repeated to transfer energy to the secondary side from the resonant circuit.

Figure 9-7. Operation in Period C

Figure 9-8. Operation in Period D

Figure 9-9. Operation in Period E

Figure 9-10. Operation in Period F

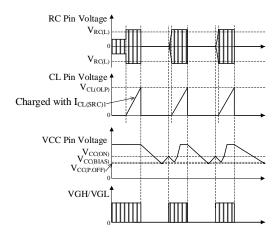

# 9.2 Startup Operation

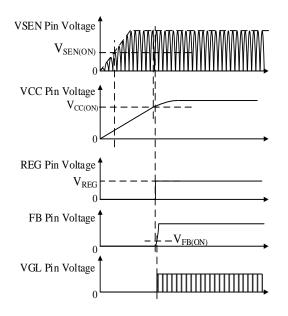

The waveform at startup is shown in Figure 9-12. When a mains input voltage is provided and the VSEN pin voltage increases to the on-threshold voltage,  $V_{\text{SEN(ON)}} = 1.200 \text{ V}$ , or more, C2 connected to the VCC pin is charged with the constant startup current,  $I_{\text{ST}}$  of 6.0 mA. When the VCC pin voltage increases to the operation start voltage,  $V_{\text{CC(ON)}} = 17.0 \text{ V}$ , the control circuit of the IC is activated. After that, when the VSEN pin voltage reaches  $V_{\text{SEN(ON)}} = 1.200 \text{ V}$  at the first-up edge of half-sinewave, the REG pin voltage is output. Then, the capacitor C9 connected to the FB pin starts to be charged. When the FB pin voltage increases to the oscillation start threshold voltage,  $V_{\text{FB(ON)}} = 0.30 \text{ V}$ , or more, the switching operation starts.

Figure 9-11. VCC Pin Peripheral Circuit

Figure 9-12. The Startup Operational Waveforms

# 9.3 Undervoltage Lockout (UVLO)

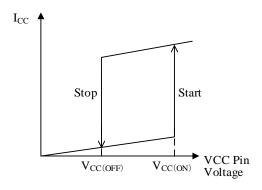

Figure 9-13 shows the relationship of  $V_{CC}$  and  $I_{CC}$ . After the IC starts operation, when the VCC pin voltage decreases to  $V_{CC(OFF)} = 8.9 \text{ V}$ , the IC stops switching operation by the undervoltage lockout (UVLO) function and reverts to the state before startup again.

Figure 9-13. V<sub>CC</sub> vs. I<sub>CC</sub>

#### 9.4 Bias Assist Function

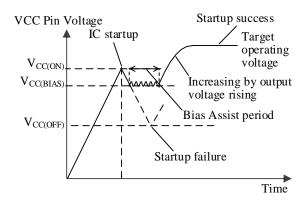

Figure 9-14 shows the VCC pin voltage behavior during the startup period.

Figure 9-14. VCC Pin Voltage during Startup Period

When the conditions of Section 9.2 are fulfilled, the IC starts operation. The circuit current,  $I_{\rm CC}$ , increases, thus the VCC pin voltage begins dropping. At the same time, the auxiliary winding voltage,  $V_{\rm D}$ , increases in proportion to the output voltage rise. Thus, the VCC pin voltage is determined by the balance between dropping due to the increase of  $I_{\rm CC}$  and rising due to the increase of the auxiliary winding voltage,  $V_{\rm D}$ .

To prevent a startup failure due to the VCC pin voltage drop, when the VCC pin voltage decreases to the startup current biasing threshold voltage,

$V_{\text{CC(BIAS)}} = 9.8 \text{ V}$ , the bias assist function is activated.

While the bias assist function is activated, any decrease of the VCC pin voltage is counteracted by

providing the startup current, I<sub>ST</sub>, from the startup circuit.

It is necessary to check the startup process based on actual operation in the application, and adjust the VCC pin voltage to prevent the startup failure.

If the VCC pin voltage decreases to  $V_{\text{CC(BIAS)}}$  and the bias assist function is activated, the power loss increases.

Thus, the VCC pin voltage in operation should be set more than  $V_{\text{CC(BIAS)}}$  by the following adjustments.

- Increase the turns ratio of the auxiliary winding to the secondary-side winding.

- Increase the value of C2 in Figure 6-1 and/or reduce the value of R1.

During all protection operations, the bias assist function is disabled.

#### 9.5 Soft-start Function

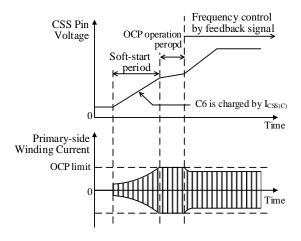

Figure 9-15 shows the soft-start operation waveforms.

Figure 9-15. Soft-start Operation

The IC has the soft-start function to reduce stress of peripheral components and prevents the capacitive mode operation.

During the soft start operation, C6 connected to the CSS pin is charged with the CSS pin charge current,  $I_{CSS(C)} = -105~\mu A$ . The oscillation frequency is varied by the CSS pin voltage. The oscillation frequency gradually decreases from  $f_{(MAX)SS}^* = 500~kHz$  at most as the CSS pin voltage rises. At the same time, the output power increases. After the output voltage increases, the IC operates with the oscillation frequency control using feedback signals.

When the IC becomes any of the following conditions, C6 is discharged with the CSS pin reset current,  $I_{CSS(R)}\!=\!1.8~\text{mA}.$

- After AC input voltage turns off, the CD pin voltage increases to V<sub>CD1</sub> = 3.0 V or more.

- Any protection operation of OVP, HVP, OLP or TSD is activated.

# 9.6 Minimum and Maximum Switching Frequency Setting

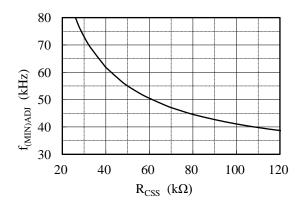

The minimum switching frequency is adjustable by setting the value of R5 ( $R_{CSS}$ ) connected to the CSS pin. The relationship of R5 ( $R_{CSS}$ ) and the externally adjusted minimum frequency,  $f_{(MIN)ADJ}$ , is shown in Figure 9-16.

The  $f_{(MIN)ADJ}$  should be adjusted to more than the resonant frequency,  $f_O$ , under the condition of the minimum mains input voltage and the maximum output power. The maximum switching frequency,  $f_{MAX}$ , is determined by the inductance and the capacitance of the resonant circuit. The  $f_{MAX}$  should be adjusted to less than the maximum frequency,  $f_{(MAX)} = 300 \text{ kHz}$ .

Figure 9-16. R5 ( $R_{CSS}$ ) vs.  $f_{(MIN)ADJ}$

### 9.7 High-side Driver

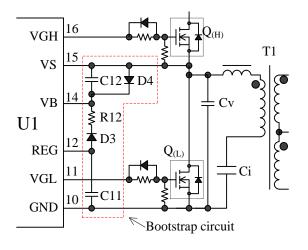

Figure 9-17 shows a bootstrap circuit. The bootstrap circuit is for driving  $Q_{(H)}$  and consists of D3, R12 and C12 between the REG pin and the VS pin.

When  $Q_{(H)}$  is OFF state and  $Q_{(L)}$  is ON state, the VS pin voltage becomes about ground level and C12 is charged via the REG pin.

When the voltage between the VB and VS pins,  $V_{B-S}$ , increases to  $V_{BUV(ON)} = 6.8 \text{ V}$  or more, the internal high-side drive circuit starts operation. When  $V_{B-S}$  decreases to  $V_{BUV(OFF)} = 6.4 \text{ V}$  or less, the drive circuit stops operation. In case the both ends of C12 and D4 are shorted, the IC is protected by  $V_{BUV(OFF)}$ . D4 is for protection against negative voltage of the VS pin

<sup>•</sup> The VCC pin voltage decreases to the operation stop voltage,  $V_{\text{CC(OFF)}} = 8.9 \text{ V}$ , or less.

<sup>\*</sup> The maximum frequency during normal operation is  $f_{(MAX)} = 300 \text{ kHz}.$

#### • D3

D3 should be an ultrafast recovery diode of short recovery time and low reverse current. When the maximum mains input voltage of the application is 265 VAC, it is recommended to use ultrafast recovery diode of  $V_{RM} = 600 \text{ V}$ .

#### • C11, C12, and R12

The values of C11, C12, and R12 are determined by total gate charge of external MOSFET, Qg, and voltage dip amount between the VB pin and the VS pin in the burst oscillation mode of the standby mode change.

C11, C12, and R12 should be adjusted so that the voltage between the VB pin and the VS is more than  $V_{BUV(ON)} = 6.8 \text{ V}$  by measuring the voltage with a high-voltage differential probe.

The reference value of C11 is 0.47  $\mu F$  to 1  $\mu F$ . The time constant of C12 and R12 should be less than 500 ns. The values of C12 and R22 are 0.047  $\mu F$  to 0.1  $\mu F$ , and 2.2  $\Omega$  to 10  $\Omega$ .

C11 and C12 should be a film type or ceramic capacitor of low ESR and low leakage current.

#### D4

D4 should be a Schottky diode of low forward voltage,  $V_F$ , so that the voltage between the VB pin and the VS pin must not decrease to the absolute maximum ratings of -0.3 V or less.

Figure 9-17. Bootstrap Circuit

# 9.8 Constant Voltage Control Operation

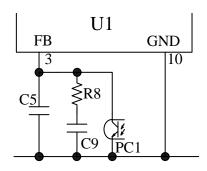

Figure 9-18 shows the FB pin peripheral circuit. The FB pin is sunk the feedback current by the photo-coupler, PC1, connected to FB pin. As a result, since the oscillation frequency is controlled by the FB pin, the output voltage is controlled to constant voltage (in inductance area).

The feedback current increases under slight load

condition, and thus the FB pin voltage decreases. While the FB pin voltage decreases to the oscillation stop threshold voltage,  $V_{FB(OFF)} = 0.20$  V, or less, the IC stops switching operation. This operation reduces switching loss, and prevents the increasing of the secondary output voltage. In Figure 9-18, R8 and C9 are for phase compensation adjustment, and C5 is for high frequency noise rejection.

The secondary-side circuit should be designed so that the collector current of PC1 is more than 195  $\mu A$  which is the absolute value of the maximum source current,  $I_{FB(MAX)}$ . Especially the current transfer ratio, CTR, of the photo coupler should be taken aging degradation into consideration.

Figure 9-18. FB Pin Peripheral Circuit

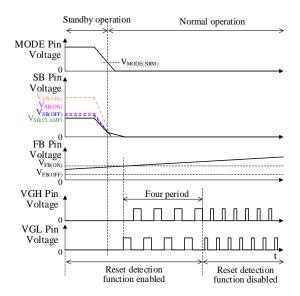

# 9.9 Standby Function

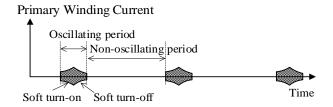

The IC has the standby function in order to increase circuit efficiency in light load. When the standby function is activated, the IC operates in the burst oscillation mode as shown in Figure 9-19.

The burst oscillation has periodic non-switching intervals. Thus, the burst oscillation mode reduces switching losses. Generally, to improve efficiency under light load conditions, the frequency of the burst oscillation mode becomes just a few kilohertz. In addition, the IC has the soft-on and soft-off functions in order to suppress rapid and sharp fluctuation of the drain current during the burst oscillation mode. thus, the audible noises can be reduced (see Section 9.9.2). The operation of the IC can be switched to the standby mode by the external signal (see Section 9.9.1).

Figure 9-19. Operational Waveform in Standby Mode

#### 9.9.1 Standby Mode Switched by External

# Signal

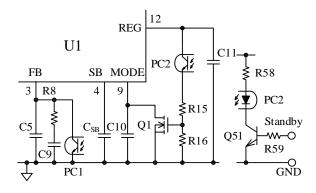

Figure 9-20 shows the standby mode switch circuit with external signal.

Figure 9-20. Standby Mode Switching Circuit

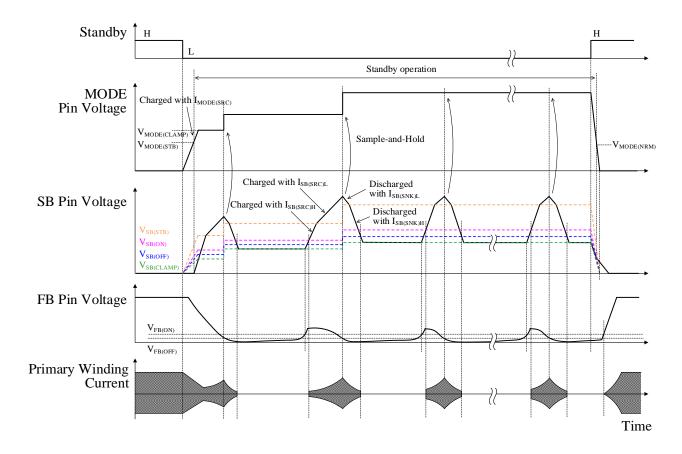

Figure 9-21 shows the standby change operation waveforms. When the standby pin of Figure 9-20 is provided with the L signal, Q1 turns off, C10 connected to the MODE pin is charged with the source current,  $I_{\text{MODE(SRC)}} = -5.0~\mu\text{A}$ , and then the MODE pin voltage increases. When the MODE pin voltage increase to the MODE Pin Standby Threshold Voltage,

$$\begin{split} &V_{MODE(STB)} = 0.5~V~or~more,~the~operation~of~the~IC~is~switched~to~the~standby~mode.~In~the~standby~mode,~the~IC~stops~a~switching~operation~while~the~following~conditions~are~fulfilled:MODE~pin~voltage <math display="inline">\geq V_{MODE(STB)}~of~0.5~V,~FB~pin~voltage \leq V_{FB(OFF)}~of~0.20~V,~and~SB~pin~voltage \leq V_{SB(OFF)}~of~V_{MODE} \times 0.50~V. \end{split}$$

When the standby input pin is provided with the high signal and the MODE pin voltage deacreases to standby release threshold voltage,  $V_{\text{MODE(NRM)}} = 0.3 \text{ V}$  or less, the IC returns to its normal operation.

Figure 9-21. Standby Mode Switching Operational Waveforms

# 9.9.2 Burst Oscillation Operation

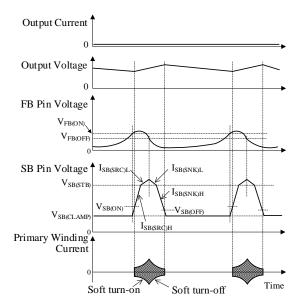

In standby operation, the IC operates burst oscillation where the peak drain current is suppressed by the soft-on /soft-off function in order to reduce audible noise from transformer. During burst oscillation operation, the switching oscillation is controlled by the SB pin voltage.

Figure 9-22 shows the burst oscillation operation waveforms.

Figure 9-22. Operational Waveforms in Burst Oscillation Mode

$V_{SB(STB)}$ ,  $V_{SB(ON)}$ ,  $V_{SB(OFF)}$ , and  $V_{SB(CLAMP)}$  are determined according to the MODE pin voltage (see Section 2).

When the FB pin voltage decreases  $V_{FB(OFF)} = 0.20$  V or less and the SB pin voltage decreases to  $V_{SB(OFF)} = V_{MODE} \times 0.50 \text{ V}$  or less, the IC stops switching operation, and then the output voltage decreases. Since the output voltage decreases, the FB pin voltage increases. When the FB pin voltage increases to the oscillation start threshold voltage,  $V_{FB(ON)} = 0.30 \text{ V}$ , C<sub>SB</sub> connected to the SB pin is charged with  $I_{SB(SRC)H} = -15 \mu A$ , and the SB pin voltage gradually increases. When the SB pin voltage increases to the oscillation start threshold voltage,  $V_{SB(ON)} = V_{MODE} \times$ 0.55 V, the IC resumes switching operation, controlling the frequency control by the SB pin voltage. Thus, the output voltage increases (Soft-on). When the SB pin voltage increases to the standby threshold voltage,  $V_{SB(STB)} = V_{MODE} \times 0.95 \text{ V}$  or more, the charging current of C<sub>SB</sub> switches to  $I_{SB(SRC)L} = -5.0 \mu A$ . After that, at the moment the FB pin voltage decreases to the oscillation stop threshold voltage,  $V_{FB(OFF)} = 0.20 \text{ V}$ , the value of the SB pin voltage is sampled and held to the MODE pin, and  $C_{SB}$  is discharged with  $I_{SB(SNK)L} = 5.0 \mu A$ . When the SB pin voltage falls below  $V_{SB(STB)} = V_{MODE} \times 0.95 \text{ V}$ ,

the CsB discharge current switches to  $I_{SB(SNK)H}=15~\mu A.$  When the SB pin voltage decreases to  $V_{SB(OFF)}$  again, the IC stops switching operation. Thus, the output voltage decreases (soft turn-off). When the SB pin voltage decreases to  $V_{SB(CLAMP)},$  the discharge of  $I_{SB(SNK)H}=15~\mu A$  stops and the SB pin voltage maintains the  $V_{SB(CLAMP)}$  value.

The SB pin discharge time in the soft turn-on/ off function depends on the value of  $C_{SB}$ . When the value of  $C_{SB}$  increases, the soft turn-on/ off function makes the peak drain current suppressed, and makes the burst period longer. Thus, the output ripple voltage may increase and/or the VCC pin voltage may decrease. If the VCC pin voltage decreases to  $V_{CC(BIAS)} = 9.8 \text{ V}$ , the bias assist function is always activated, and it results in the increase in power loss (see Section 9.4).

Thus, it is necessary to adjust the value of  $C_{SB}$  during checking the input power, the output ripple voltage, and the VCC pin voltage. The reference value of  $C_{SB}$  is about 100 pF to 0.01  $\mu$ F.

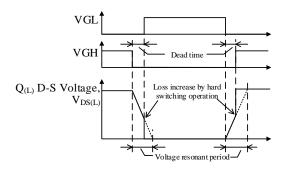

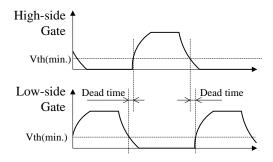

# 9.10 Automatic Dead Time Adjustment Function

The dead time is the period when both the high-side and the low-side power MOSFETs are off.

As shown in Figure 9-23, if the dead time is shorter than the voltage resonant period, the power MOSFET is turned on and off during the voltage resonant operation. In this case, the power MOSFET turned on/off in hard switching operation, and the switching loss increases.

Figure 9-23. ZVS Failure Operation Waveform

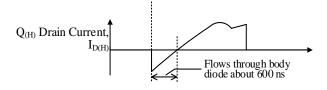

The automatic dead time adjustment function is the function that the ZVS (Zero Voltage Switching) operation of  $Q_{(H)}$  and  $Q_{(L)}$  is controlled automatically by the voltage resonant period detection of IC. The voltage resonant period is varied by the power supply specifications (input voltage and output power, etc.). However, the power supply with this function is unnecessary to adjust the dead time for each power supply specification.

As shown in Figure 9-24, the VS pin detects the dv/dt period of rising and falling of the voltage between drain

and source of the low-side power MOSFET,  $V_{DS(L)}$ , and the IC sets its dead time to that period. This function controls so that the high-side and the low-side power MOSFETs are automatically switched to Zero Voltage Switching (ZVS) operation. This function operates in the period from  $t_{d(MIN)} = 0.24~\mu s$  to  $t_{d(MAX)} = 1.65~\mu s$ .

In minimum output power at maximum input voltage and maximum output power at minimum input voltage, the ZCS (Zero Current Switching) operation of IC (the drain current flows through the body diode is about 600 ns as shown in Figure 9-25), should be checked based on actual operation in the application.

Figure 9-24. VS Pin and Dead Time Period

Figure 9-25. ZCS Check Point

#### 9.11 Capacitive Mode Detection Function

The resonant power supply is operated in the inductance area shown in Figure 9-26. In the capacitance area, the power supply becomes the capacitive mode operation (see Section 9.1). In order to prevent the operation, the minimum oscillation frequency is generally needed to be set higher than  $f_0$  on each power supply specification. However, the IC has the capacitive mode operation detection function kept the frequency higher than  $f_0$ . Thus, the minimum oscillation frequency setting is unnecessary and the power supply design is easier. In addition, the ability of transformer is improved because the operating frequency can operate close to the resonant frequency,  $f_0$ .

The resonant current is detected by the RC pin, and the IC prevents the capacitive mode operation. When the capacitive mode is detected, C7 connected to the CL pin is charged with  $I_{\text{CL(SRC)1}} = -17~\mu\text{A}$ . C6 connected to the CSS pin is discharged with a sink current,

$I_{CSS(H)} = 20.5$  mA. This results in an increase in the

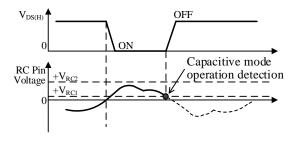

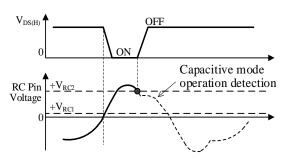

switching frequency and suppression of capacitive mode operation. When the CL pin voltage increases to  $V_{\text{CL(OLP)}}$ , the OLP is activated and the switching operation stops. During the OLP operation, the intermittent operation by UVLO is repeated (see Section 9.18). The detection voltage is changed to  $V_{\text{RC1}} = \pm 0.10 \text{ V}$  or  $V_{\text{RC2}} = \pm 0.50 \text{ V}$  depending on the load as shown in Figure 9-28 and Figure 9-29. The capacitive mode operation detection function operations as follows:

#### • Q<sub>(H)</sub> Turn-on Period

Figure 9-27 shows the RC pin waveform in the inductance area, and Figure 9-28 and Figure 9-29 shows the RC pin waveform in the capacitance area. In the inductance area, the RC pin voltage doesn't cross the plus side detection voltage in the downward direction during the on period of  $Q_{(H)}$  as shown in Figure 9-27. On the contrary, in the capacitance area, the RC pin voltage crosses the plus side detection voltage in the downward direction. At this point, the capacitive mode operation is detected. Thus,  $Q_{(H)}$  is turned off, and  $Q_{(L)}$  is turned on, as shown in Figure 9-28 and Figure 9-29.

#### • Q<sub>(L)</sub> Turn-on Period

Contrary to the above of  $Q_{(H)}$ , in the capacitance area, the RC pin voltage crosses the minus side detection voltage in the upward directiont during the on period of  $Q_{(L)}$  At this point, the capacitive mode operation is detected. Thus,  $Q_{(L)}$  is turned off and  $Q_{(H)}$  is turned on.

As above, since the capacitive mode operation is detected by pulse-by-pulse and the operating frequency is synchronized with the frequency of the capacitive mode operation, and the capacitive mode operation is prevented. In addition to the adjusting method of  $R_{\rm OCP},$  C3, and R6 in Section 9.17,  $R_{\rm OCP},$  C3, and R6 should be adjusted so that the absolute value of the RC pin voltage increases to more than  $|V_{RC2}|=0.50~V$  under the condition caused the capacitive mode operation easily, such as startup, turning off the mains input voltage, or output shorted. The RC pin voltage must be within the absolute maximum ratings of -6 to 6~V.

Figure 9-26. Operating Area of Resonant Power Supply

Figure 9-27. RC Pin Voltage in Inductance Area

Figure 9-28. High-side Capacitive Mode Detection in Light Load

Figure 9-29. High-side Capacitive Mode Detection in Heavy Load

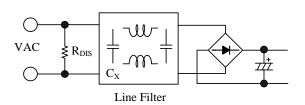

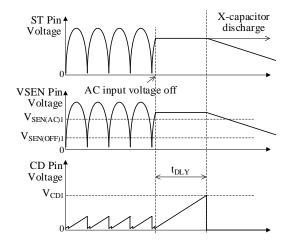

#### 9.12 X-Capacitor Discharge Function

Generally, the line filter is set in the input circuit part of power supply as shown in Figure 9-30.

As per IEC 62368-1 safety requirements, the voltage across the capacitor of line filter (i.e., X-capacitor,  $C_X$ ) of  $\geq 300$  nF must be decreased to 60 V or less within 2 seconds after AC input voltage cutoff. Thus, the discharge resistor,  $R_{DIS}$ , is connected in parallel with  $C_X$ . While the AC input voltage is applied,  $R_{DIS}$  consumes power at all time. The dissipation power of  $R_{DIS}$ ,  $P_{RDIS}$ , is calculated as follows:

$$P_{RDIS} = \frac{V_{AC(RMS)}^2}{R_{DIS}}$$

(7)

where,  $V_{AC(RMS)}$  is the effective value of AC input voltage.

When the combined resistance of  $R_{DIS}$  is 1  $M\Omega$  and the AC input voltage is 265 V,  $P_{RDIS}$  becomes about 70 mW.

Figure 9-30. Typical Line Filter Circuit

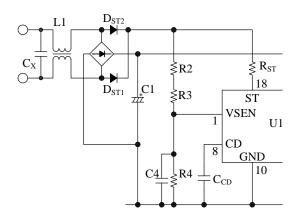

In order to remove  $R_{ST}$  and improve the circuit efficiency, the IC has the X-capacitor discharge function. As shown in Figure 9-31,  $D_{ST1}$ ,  $D_{ST2}$  and  $R_{ST}$  are connected to the ST pin from AC input line.

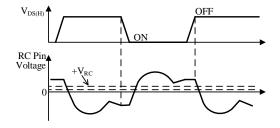

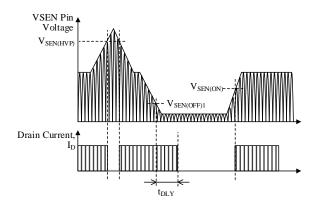

When the AC voltage is input and the VSEN pin voltage reaches  $V_{\text{SEN(ON)}}$  = 1.200 V at startup, the IC starts.

Then, following half-sinewaves are detected by two threshold voltages of the VSEN pin,  $V_{\text{SEN(OFF)1}} = 1.000 \text{ V}$  or  $V_{\text{SEN(AC)1}} = 2.70 \text{ V}$  (see Figure 9-32). Thus the IC's X-capacitor discharge function achieves the wide range detection for universal specification.

When the AC input voltage is cut off, the VSEN pin voltage becomes practically constant and the VSEN pin cannot detect the both threshold,  $V_{SEN(OFF)1}$  and  $V_{SEN(AC)1}$ . Then, the CD pin capacitor,  $C_{CD}$ , is discharged with  $I_{CD(SRC)} = -10.2~\mu A,$  and the CD pin voltage increases. When the CD pin voltage reaches  $V_{CD1} = 3.0~V,$  the X-capacitor is discharged with the constant current,  $I_{ST} = 6.0~mA.$

When the VSEN pin voltage becomes  $V_{SEN(OFF)1}$  or  $V_{SEN(AC)1}$ , each internal threshold voltage becomes  $V_{SEN(OFF)2} = 0.8 \ V$  or  $V_{SEN(AC)2} = 2.4 \ V$  automatically.

Thus, the input voltage can be detected stably.

Figure 9-31. ST Pin Peripheral Circuit

Figure 9-32. Operational Waveform of X-capacitor Discharge Function

The time until the CD pin voltage reaches  $V_{\text{CD1}}$  from the cutoff of AC input voltage is delay time,  $t_{\text{DLY}}$ .

The maximum value of  $t_{DLY}$ ,  $t_{DLY\_MAX}$ , can be set by the capacitor of the CD pin and is calculated by Equation (9) in Section 9.16.2.

The recommend value of  $R_{ST}$  is 5.6 k $\Omega$  to 10 k $\Omega$ .  $R_{ST}$  is applied high voltage and are high resistance, the following should be considered according to the requirement of the application:

- Select a resistor designed against electromigration, or

- Use a combination of resistors in series for that to reduce each applied voltage

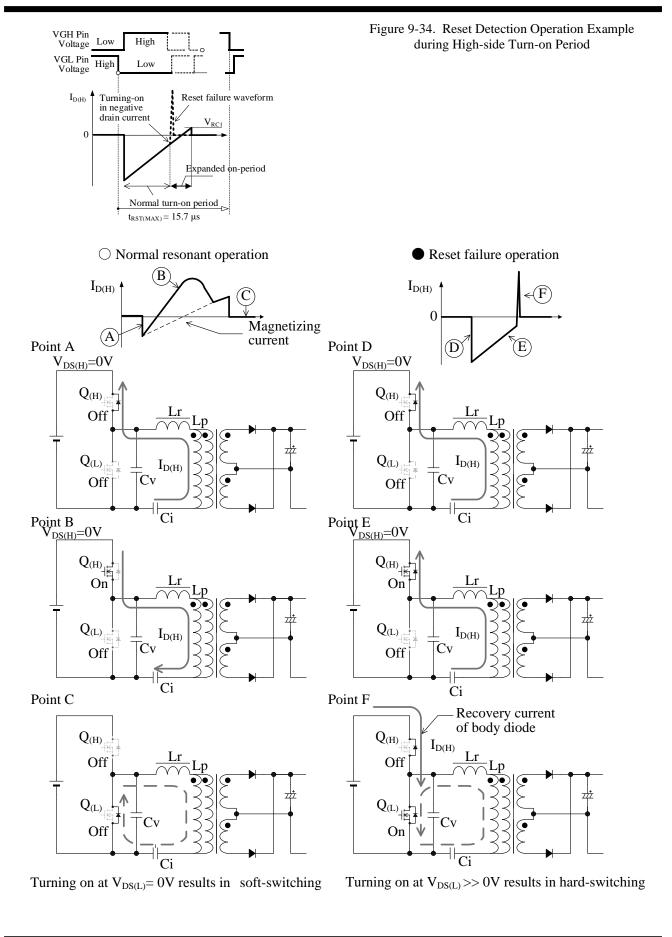

#### 9.13 Reset Detection Function

In the startup period, the feedback control for the output voltage is inactive. If a magnetizing current may not be reset in the on-period because of unbalanced operation, a negative current may flow just before a power MOSFET turns off. This causes a hard switching

operation, increases the stresses of the power MOSFET. Where the magnetizing current means the circulating current applied for resonant operation, and flows only into the primary-side circuit. To prevent the hard switching, the IC has the reset detection function. The reset detection function is enabled in any of the following conditions.

- $\bullet \ V_{CSS} < 1.5 \ V$

- $\bullet \ V_{CSS} < V_{FB}$

- during standby operation

- in 4 cycles of V<sub>GH</sub>/V<sub>GL</sub> immediately after switching from standby operation to normal operation (see Figure 9-33)

- during normal operation, in 4 cycles of  $V_{GH}/V_{GL}$  immediately after the FB pin voltage becomes  $\geq$   $V_{FB(ON)}$  from  $\leq V_{FB(OFF)}$  and resumes oscillating

Figure 9-33. Timing for Enabling/Disabling Reset Detection Function (Shifting from Standby to Normal Operation)

Figure 9-35 shows the high-side operation and the reference drain current waveforms in a normal resonant operation and a reset failure operation. To prevent the hard switching operation, the reset detection function operates such as an on period is extended until the absolute value of a RC pin voltage,  $|V_{RCI}|$ , increases to 0.10 V or more. When the on period reaches the maximum reset time,  $t_{RST(MAX)} = 15.7~\mu s$ , the on-period expires at that moment, i.e., the power MOSFET turns off (see Figure 9-34).

# **SSC3S927A**

Figure 9-35. Reference High-side Operation and Drain Current Waveforms in Normal Resonant Operation and in Reset Failure Operation

# 9.14 Overvoltage Protection (OVP)

When the voltage between the VCC pin and the GND pin is applied to the OVP threshold voltage,  $V_{\text{CC(OVP)}} = 32.0 \text{ V, or more, the overvoltage protection} \\ \text{(OVP)} \text{ is activated, and the IC stops switching operation} \\ \text{in protection mode. When the OVP activates, the bias} \\ \text{assist function is disabled and the VCC pin voltage} \\ \text{decreases. Then the VCC pin voltage decreases to} \\ V_{\text{CC(P.OFF)}} = 8.9 \text{ V, the undervoltage lockout (UVLO)} \\ \text{function is activated, and the IC reverts to the state} \\ \text{before startup again.} \\$

After that, the startup circuit activates, and the VCC pin voltage increases to  $V_{\rm CC(ON)} = 17.0$  V, and the IC starts operation. During the protection mode, restart and stop are repeated. When the fault condition is removed, the IC returns to normal operation automatically. When the auxiliary winding supplies the VCC pin voltage, the OVP is able to detect an excessive output voltage, such as when the detection circuit for output control is open in the secondary-side circuit because the VCC pin voltage is proportional to the output voltage.

The output voltage of the secondary-side circuit at OVP operation,  $V_{\text{OUT(OVP)}}$ , is approximately given as below:

$$V_{OUT(OVP)} = \frac{V_{OUT(NORMAL)}}{V_{CC(NORMAL)}} \times 32(V)$$

(8)

where,  $V_{OUT(NORMAL)}$  is output voltage in normal operation, and  $V_{CC(NORMAL)}$  is VCC pin voltage in normal operation

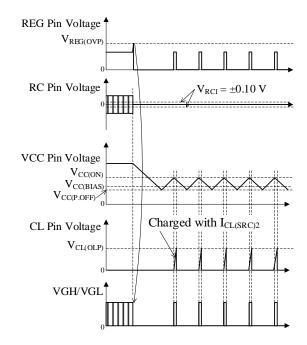

# 9.15 REG Overvoltage Protection (REG\_OVP)

The IC has the REG overvoltage protection (REG\_OVP) for the overvoltage of the REG pin. Figure 9-36 shows the REG\_OVP operational waveforms.

When the REG pin voltage increases to REG Pin OVP Threshold Voltage,  $V_{\text{REG(OVP)}} = 12.4 \text{ V}$ , the REG\_OVP is activated, and the IC stops switching operation and fixes the REG pin voltage to ground level.

When the REG\_OVP activates, the bias assist function is disabled and the VCC pin voltage decreases. Then the VCC pin voltage decreases to  $V_{\text{CC(P.OFF)}} = 8.9 \text{ V}$ , the undervoltage lockout (UVLO) function is activated, and the IC reverts to the state before startup again.

After that, the startup circuit activates, and the VCC pin voltage increases. When the VCC pin voltage reaches  $V_{\text{CC(ON)}} = 17.0 \text{ V}$ , the IC starts operation and the VCC pin voltage decreases. When the VCC pin voltage decreases to  $V_{\text{CC(BIAS)}}$ , FB pin voltage increases and switching operation starts.

When the switching operation starts at RC pin voltage

within  $V_{RC1} = \pm 0.10$  V, C7 connected to CL pin is rapidly charged with  $I_{CL(SRC)2} = -135$   $\mu A$ . When the CL pin voltage reaches  $V_{CL(OLP)} = 4.2$  V, the IC stops switching operation and restarts after decreasing to  $V_{CC(OFF)}$ .

In this way, the intermittent operation by the CL pin protection and the UVLO is repeated.

When the fault condition is removed, the IC returns to normal operation automatically.

Figure 9-36. REG\_OVP Operational Waveform

# 9.16 Input Voltage Protection

This function has the following:

- Input High-voltage Protection (HVP)

- Input Undervoltage Protection (UVP)

This function turns on and off switching operation according to the VSEN pin voltage detecting the AC input voltage, and thus prevents excessive input current and over heating. Section 9.16.1 shows HVP, Section 9.16.2 shows UVP. Figure 9-37 shows the pherepheral circuit of VSEN pin. Figure 9-38 shows the input voltage protection operational waveforms.

# 9.16.1 Input High-voltage Protection (HVP)

When the AC input voltage increases from steady state and the VSEN pin voltage reaches  $V_{\text{SEN(HVP)}} = 5.6 \text{ V}$  or more, the input high-voltage protection (HVP) activates and the IC stops switching operation. During the HVP operation, the intermittent operation by UVLO is repeated (see Section 9.14). After that, when the AC input voltage decreases and the VSEN pin voltage falls to  $V_{\text{SEN(HVP)}}$  or less, the IC starts

switching operation.

# 9.16.2 Input Undervoltage Protection (UVP)

Even if the IC is in the operating state that the VCC pin voltage is  $V_{\text{CC(OFF)}}$  or more, when the AC input voltage decreases from steady-state and the VSEN pin voltage falls to  $V_{\text{SEN(OFF)}1}$  = 1.000 V or less for the delay time,  $t_{\text{DLY}}$ , the IC stops switching operation.

When the AC input voltage increases and the VSEN pin voltage reaches  $V_{\text{SEN(ON)}} = 1.200 \text{ V}$  or more in the operating state that the VCC pin voltage is  $V_{\text{CC(OFF)}}$  or more, the IC starts switching operation.

The maximum delay time,  $t_{DLY\_MAX}$ , can be calculated by Equation (9).

$$t_{DLY\_MAX} = \frac{V_{CD1} \times C_{CD}}{\left|I_{CD(SRC)}\right|}$$

(9)

Where.

V<sub>CD1</sub> is CD Pin Threshold Voltage 1 (3.0 V),

$C_{CD}$  is the capacitance value of CD pin connected capacitor (about  $0.1\mu F$  to  $0.47\mu F), and$

$I_{CD(SRC)}$  is CD Pin Source Current (-10.2  $\mu$ A)

For example, if  $C_{CD}$  is  $0.1\mu F$ ,

$$t_{DLY\_MAX} = \frac{3.0 \text{ V} \times 0.1 \mu F}{\left|-10.2 \text{ } \mu A\right|} \approx 29.4 \text{ ms}$$

Neglecting the effect of both input resistance and forward voltage of rectifier diode, the effective value of AC input voltage when HVP and UVP are activated is calculated as follows:

$$V_{AC(OP)} = \frac{1}{\sqrt{2}} \times V_{SEN(TH)} \times \left(1 + \frac{R2 + R3}{R4}\right)$$

(10)

where,

$V_{\text{DC(OP)}}$  is the effective value of AC input voltage when HVP and UVP are activated, and

$V_{\text{SEN(TH)}}$  is any one of threshold voltage of VSEN pin (see Table 9-1).

Table 9-1. VSEN Pin Threshold Voltage

| Parameter                        | Symbol                 | Value<br>(Typ.) |

|----------------------------------|------------------------|-----------------|

| VSEN Pin HVP Threshold Voltage   | V <sub>SEN(HVP)</sub>  | 5.6 V           |

| VSEN Pin Threshold Voltage (On)  | V <sub>SEN(OFF)1</sub> | 1.000 V         |

| VSEN Pin Threshold Voltage (Off) | V <sub>SEN(ON)</sub>   | 1.200 V         |

Because R2 and R3 are applied high voltage and are high resistance, the following should be considered:

- Select a resistor designed against electromigration according to the requirement of the application, or

- Use a combination of resistors in series for that to reduce each applied voltage.

The reference value of R2 is about 10 M $\Omega$ .

C4 shown in Figure 9-37 is for reducing noises. The value is 1000 pF or more, and the reference value is about  $0.01 \, \mu F$ .

The value of R2, R3 and R4 and C4 should be selected based on actual operation in the application.

Figure 9-37. VSEN Pin Pherepheral Circuit

Figure 9-38. Input Voltage Protection Operational Waveforms

#### 9.17 Overcurrent Protection (OCP)

The overcurrent protection (OCP) detects the drain current,  $I_D$ , on pulse-by-pulse basis, and limits output power.

In Figure 9-39, this circuit enables the value of C3 for shunt capacitor to be smaller than the value of Ci for current resonant capacitor, and the detection current through C3 is small. Thus, the loss of the detection resistor,  $R_{\rm OCP}$ , is reduced, and  $R_{\rm OCP}$  is a small-sized one available.

There is no convenient method to calculate the accurate resonant current value according to the mains input and output conditions, and others. Thus,  $R_{OCP}$ , C3, and C6 should be adjusted based on actual operation in the application. The following is a reference adjusting method of  $R_{OCP}$ , C3, R6, and C8:

C3 and R<sub>OCP</sub>

C3 is 100pF to 330pF (around 1 % of Ci value).  $R_{\rm OCP}$  is around 100  $\Omega.$

Given the current of the high side power MOSFET at ON state as  $I_{D(H)}$ .  $R_{OCP}$  is calculated by Equation (11). The detection voltage of  $R_{OCP}$  is used for the detection of the capacitive mode operation (see Section 9.11). Therefore, setting of  $R_{OCP}$  and C3 should be taken account of both OCP and the capacitive mode operation.

$$R_{OCP} \approx \frac{\left|V_{RC(L)}\right|}{I_{D(H)}} \times \left(\frac{C3 + Ci}{C3}\right) \tag{11}$$

• R6 and C8 are for high frequency noise reduction. R6 is  $100~\Omega$  to  $470~\Omega$ . C8 is 100~pF to 1000~pF.

Figure 9-39. RC Pin Peripheral Circuit

The OCP operation has two types as follows:

Overcurrent Protection 1 (OCP1)

When the current flowing through the power

MOSFET increases and the absolute value of the RC

pin voltage exceeds  $|V_{RC(H)}| = 2.80 \text{ V}$ , the OCP1 is activated. Then, the on/off states of power MOSFETs are inverted. At the same time, C6 is discharged with  $I_{CSS(H)} = 20.5 \text{ mA}$ , and the switching frequency increases rapidly to suppress the output power. When the RC pin voltage decreases to  $|V_{RC(H)}|$  or less, the discharge is stopped.

#### 2) Overcurrent Protection 2 (OCP2)

This OCP2 is activated in startup, restart, and standby operation.

When the current through the power MOSFET increases and the absolute value of the RC pin voltage exceeds  $|V_{RC(L)}| = 1.90 \text{ V}$ , the OCP2 is activated. Then, the IC discharges C6 connected to the CSS pin with the sink current,  $I_{CSS(L)} = 1.8$  mA. This increases the switching frequency to suppress the output power. If the absolute value of RC pin voltage decreases to  $|V_{RC(L)}|$  during the C6 discharge, the IC stops the discharge.

# 9.18 Overload Protection (OLP)

Figure 9-40 shows the overload protection (OLP) waveforms.

When the current flowing through the power MOSFET increases along with a rise in the output load, causing the absolute value of the RC pin voltage to exceed  $|V_{RC(L)}| = 1.90 \text{ V}$ , the IC enters an overload detection state.

In an overload detection state, the C7 connected to the CL pin is charged with  $I_{\text{CL(SRC)1}} = -17 \, \mu\text{A}$ . When the overload detection state continues and the CL pin voltage increases to  $V_{\text{CL(OLP)}}$ , the OLP is activated.

When the CL pin voltage becomes the threshold voltage of OLP,  $V_{\text{CL(OLP)}} = 4.2 \text{ V}$ , the OLP is activated and the switching operation stops. During the OLP operation, the intermittent operation by UVLO is repeated (see Section 9.14). When the fault condition is removed, the IC returns to its normal operation automatically.

Figure 9-40. OLP Operational Waveform

# 9.19 Thermal Shutdown (TSD)

When the junction temperature of the IC reach to the Thermal Shutdown Temperature  $T_{J(TSD)} = 140~^{\circ}\text{C}$  (min.), Thermal Shutdown (TSD) is activated and the IC stops switching operation. When the VCC pin voltage is decreased to  $V_{CC(P.OFF)} = 8.9~\text{V}$  or less and the junction temperature of the IC is decreased to less than  $T_{J(TSD)}$ , the IC restarts.

During the protection mode, restart and stop are repeated. When the fault condition is removed, the IC returns to its normal operation automatically.

#### 10. Design Notes

### 10.1 External Components

Take care to use the proper rating and proper type of components.

# 10.1.1 Input and output electrolytic capacitors

Apply proper derating to a ripple current, a voltage, and a temperature rise. It is required to use the high ripple current and low impedance type electrolytic capacitor that is designed for switch mode power supplies.

# 10.1.2 Resonant transformer

The resonant power supply uses the leakage inductance of a transformer. Therefore, to reduce the effect of the eddy current and the skin effect, the wire of transformer should be used a bundle of fine litz wires.

#### 10.1.3 Current detection resistor, Rocp

To reduce the effect of the high frequency switching current flowing through  $R_{\text{OCP}}$ , choose the resister of a low internal inductance type. In addition, its allowable dissipation should be chosen suitable.

#### 10.1.4 Current resonant capacitor, Ci

Since a large resonant current flows through Ci, Ci should be used a low loss and a high current capability capacitor such as a polypropylene film capacitor. In

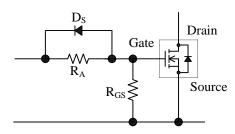

addition, Ci must be taken into account its frequency characteristic because a high frequency current flows.